The IEEE Solid State Circuits Society has the audio program Chip Chat that is about the people making integrated circuits. Presently, there are two podcast featuring interviews with:

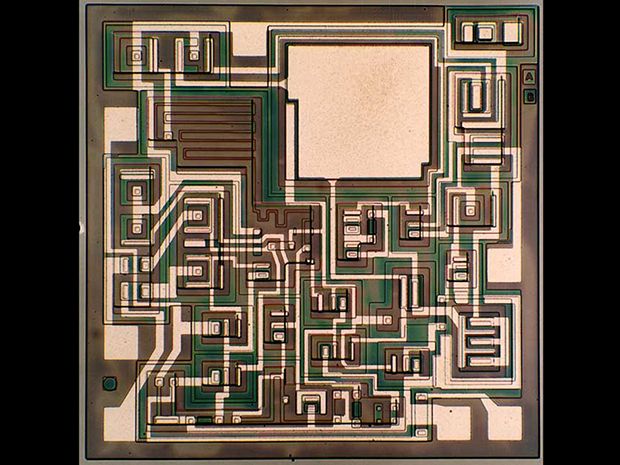

- Dr Albert Theuwissen the CEO and Founder of Harvest Imaging and a part-time professor at TU Delft where he coaches PhD students and researches CMOS image sensors.

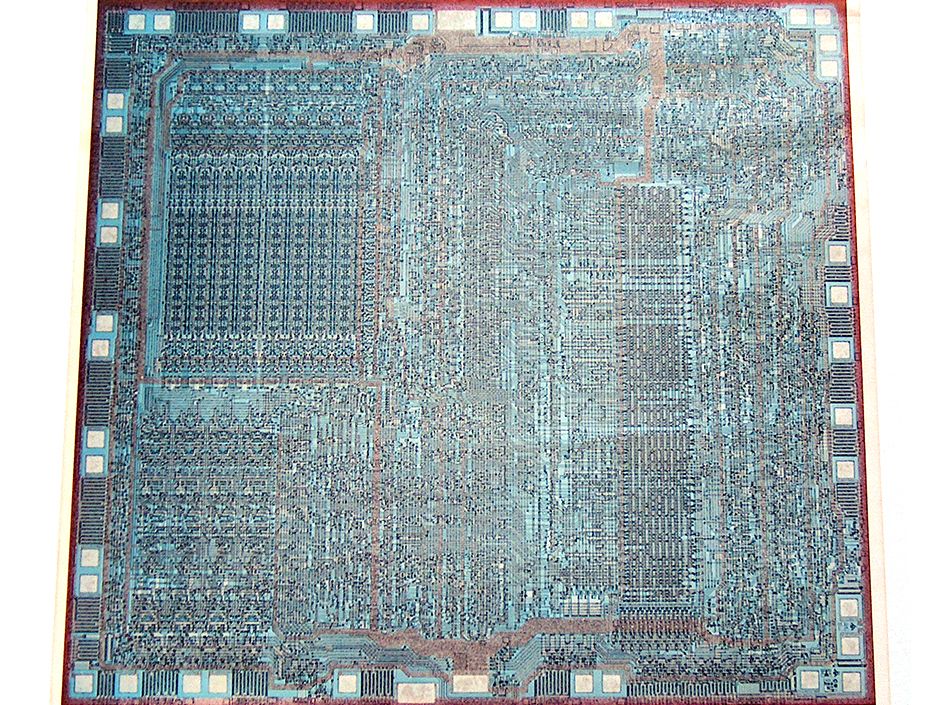

- Dr Gert Cauwenberghs the Professor of Bioengineering and Co-Director of the Institute for Neural Computation at UC San Diego, La Jolla CA.